FOPLP (Fan-Out Panel Level Packaging)

by bptek

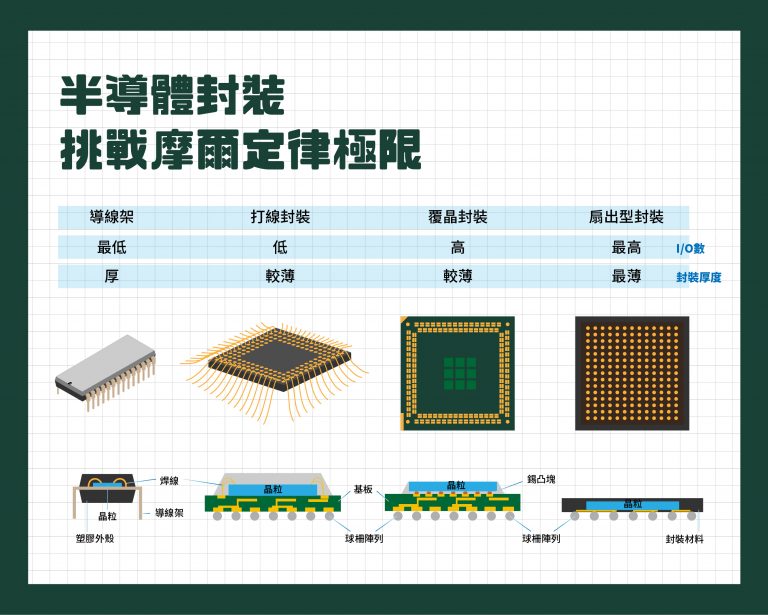

先進封裝是半導體產業發展的重要趨勢, 它能夠在更小的體積內實現更高的性能、更低的功耗和更強大的功能。它推動摩爾定律的延伸,也為下一代電子產品的設計和製造帶來了新的可能性。 這對於推動人工智慧(AI)、高效能運算(HPC)等新興應用至關重要。目前主流的12吋300 mm晶圓可能幾年後就無法有效率地封裝先進AI晶片,因此封裝形式不斷演進,未來先進封裝的市場規模將持續擴大。

<< used semiconductor equipment >>

先進封裝常見代表:「覆晶封裝」Flip-Chip、「2.5D/3D IC封裝」 CoWoS、「扇出型封裝」Fan-Out Packaging等類型。

(圖片來源:經濟部產業技術司)

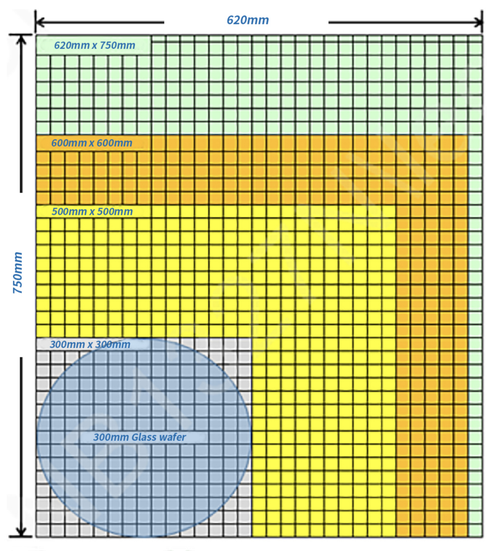

FOPLP扇出型面板級封裝(Fan-Out Panel Level Packaging),是一種先進的半導體封裝技術。 它在扇出型封裝(Fan-Out Packaging)的基礎上,將傳統的圓形晶圓基板改為方形面板基板(例如玻璃基板),以提高封裝密度和利用率,降低成本。 FOPLP 的方形面積使用率超過 95%。方形面板的基板面積比傳統12吋(300mm)晶圓有著更大面積,多達6倍,顯著提升晶片製作效率。FOPLP有效提供封裝過程的材料利用,降低切割產生邊邊角角的浪費成本。

(圖片來源:群創)

CoWoS 封裝技術主要應用於先進製程,而FOPLP 主攻成熟制程高性價比領域,適用於多種需要高功率、低功耗和大電流的應用,例如智慧手機、汽車電子與物聯網設備等,包含電源管理IC(PMIC)、感測器、功率IC、射頻和連接模組等。與CoWoS封裝相比,FOPLP的優勢在於其使用「方形」基板封裝IC,能達到更高的利用率。由於面板面積遠大於12吋晶圓,FOPLP主要技術挑戰在於面板翹曲變形、均勻性與良率等。隨著材料改良、技術進步,FOPLP愈來愈成熟,即將開創更大的市場。