CoWoS(Chip-on-Wafer-on-Substrate)是一種半導體先進的2.5D/3D封裝技術。封裝的主要功能具有保護、散熱與導通,而 ”先進” 封裝,主要是針對 7nm 以下晶圓的封裝技術,即用於高性能和高密度整合的系統級封裝,例如AI晶片、超級電腦、5G、車用電子等。

<< used semiconductor equipment >>

CoWoS帶來的好處包括:

- 縮短晶片距離、超高速傳輸、延遲大幅降低,較傳統封裝降低30%以上。

- 異質相容性:支援不同製程的晶片(如14nm邏輯晶片與28nm HBM)整和.

- 高密度整合:單封裝可整合多個SOC和HBM,例如CoWoS-S5支持8個HBM3和2個SOC,電晶體密度提升20倍。

- 模組再擴充。CoWoS-L 技術透過 LSI(局部矽互連)晶片,能堆疊多達 12 個 HBM4 記憶體堆疊,滿足未來 AI 模型需求.

- CoWoS 將距離壓縮至毫米級,能耗下降,散熱性能好。TSV 結構搭配微流道冷卻技術,散熱效率提升 40%有助於維持系統的穩定運行,可採用新型非凝膠TIM,導熱係數大於20w/k。

CoWoS流程

可以分成「CoW」和「WoS」:

- CoW全名為「Chip-on-Wafer」,是指將晶片堆疊的技術。

- WoS全名為「Wafer-on-Substrate」,是指將堆疊好的晶片封裝到基板上的技術。

因此,CoWoS的意思就是把晶片堆疊起來,並封裝在基板上,此封裝技術的好處是能夠減少晶片的空間,同時還能減少功耗與成本。

Chip-on-Wafer階段

微凸塊連接:將邏輯晶片(如GPU、CPU)與高頻寬記憶體(HBM)通過微凸塊(μbump)連接至矽中介層(interposer),間距可低至20μm。 底部填充:使用環氧樹脂等材料填充晶片與中介層間隙,緩解熱應力,提高封裝的可靠性和穩定性。

Wafer-on-Substrate階段

基板鍵合:將帶有晶片和中介層的晶圓與臨時基板結合,然後進行化學機械拋光(CMP)減薄至50μm以下,方便後續處理。

系統整合階段

切割與封裝:將晶圓切割為單顆晶片,去除臨時基板後,將晶片與封裝基板鍵合併注入熱介面材料(TIM),確保散熱效率,完成最終的封裝。

CoWoS依照晶片和基板間的中介層主要分成三種

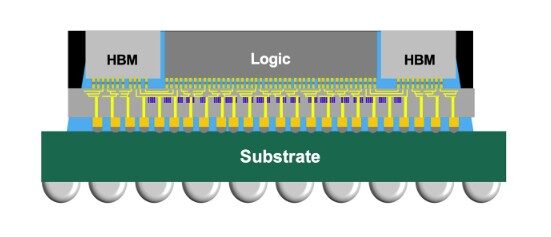

CoWoS-S:矽中介層(Silicon Interposer)

特點:目前主流,採用單片矽中介層,TSV密度高。連線密度最高(微凸塊間距 30-60μm),頻寬達 3.35TB/s,延遲最低。CoWoS-S成本最高,產能有限,最大約可達2700mm2;且良率受限於中介層尺寸,尺寸越大良率越低。每片封裝破千美元。

應用:NVIDIA A100/H100 GPU、GOOGLE TPU等AI晶片。

(圖片來源:tsmc)

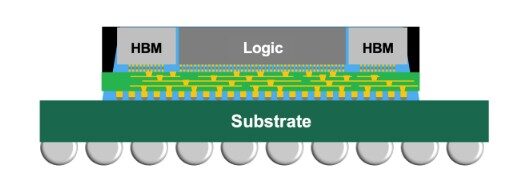

CoWoS-R:重分佈線中介層,RDL(Redistribution Layer)

特點:以由聚合物和銅線組成(RDL)替代矽中介層,通過RDL實現細間距佈線,可靠性更高,成本比CoWoS-S 低 40%。避免了矽中介層的熱膨脹係數不匹配問題,封裝尺寸彈性大,產能較高。每片封裝700~900美元。

應用:網路通信領域的5G基站、光模組整合,邊緣AI伺服器。

(圖片來源:tsmc)

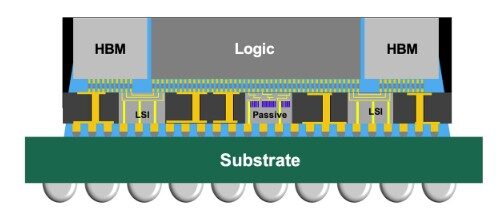

CoWoS-L:LSI + RDL中介層 (局部矽互連)

特點:融合了CoWoS-S和CoWoS-R的技術優點,使用RDL中介層與局部矽互連(LSI,Local Silicon Interconnect),支援3倍光罩尺寸,提升產品設計的靈活性,能堆疊最多HBM和SOC,預計成為未來主流,成本優於 S 型。每片封裝900~1100美元 應用:新一代AI晶片。

(圖片來源:tsmc)

<< Product >>